集成化浪潮下的增长与挑战

一、系统级封装(SiP)行业概况

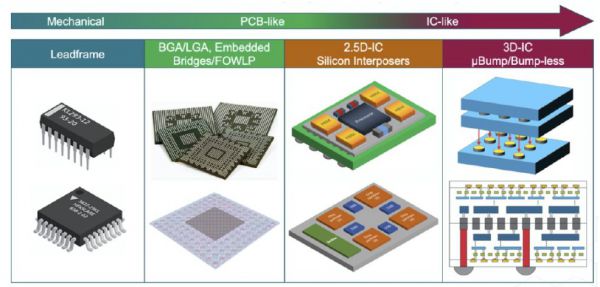

系统级封装(System-in-Package,SiP)技术是一种将多个功能模块、集成电路芯片、被动元件等集成在一个封装体内的先进封装技术。与传统的封装技术相比,SiP技术具有更高的集成度、更小的体积、更低的功耗和更高的性能。SiP封装通过将多个芯片或组件封装在一起,满足电子系统的功能集成,从而在电子设备中实现轻薄化、高性能和低功耗的目标。SiP按组装方式可以简单分为2D、2.5D、3D。

图1 封装技术演变

作为后摩尔时代的关键技术,系统级封装(SiP)通过异质集成不同功能的芯片与无源器件,推动电子产品向小型化、高性能化发展。SiP系统级封装技术逐渐成为电子技术发展的前沿热点,市场需求持续扩容,目前我国SiP行业正处于市场成长期。数据显示,2023年中国SiP行业市场规模为371.2亿元,其中2D封装占78.05%,2.5D/3D封装合计占比约20%[1]。2024年中国SiP行业市场规模增长至450亿元[1]。当前,SiP封装技术正从传统单/双面的FC、WB或hybrid封装、单面Fan-out封装技术向2.5D/3D封装和模组化解决方案转变。同时,SiP基板技术也不断开发出更薄的基板,采用超薄基板和背面凹腔工艺来减少封装厚度。相关的贴片设备也从追求高产出转向高精度的贴装技术。未来,随着封装技术的不断进步,SiP产品的集成度和性能将进一步提升。

二、三维异质异构集成概述

三维异质异构集成是将不同材料、不同结构、不同功能的芯片或元件,通过三维的方式集成在一起,形成一个具有特定功能和性能的系统。三维异质异构集成具有高密度集成、异质异构集成、系统级优化等特点,实现了芯片之间的异质性和异构性,以及在三维空间内的集成,打破传统集成电路制造中对单一衬底材料、单一工艺流程的依赖,实现芯片间无缝互连,综合提高系统性能和集成度。

1)高密度互连,通过三维堆叠和互连技术,能够在有限的芯片面积内集成更多的功能单元。实现更高的集成度,满足电子设备对小型化、高性能的需求。

2)异质异构集成,可以将不同材料、不同工艺制造的芯片或器件集成在一起,如将硅基芯片与化合物半导体芯片(如GaAs、GaN等)集成,充分发挥各自的优势,实现功能互补。

3)系统级优化,从系统层面进行优化设计,考虑芯片之间的互连、信号传输、电源管理等,提高系统的整体性能和可靠性。

三、三维异质异构集成的应用场景

1)高性能计算与人工智能,通过将多个不同功能的芯片(如CPU、GPU、FPGA等)进行三维异质集成,能够构建出高性能计算平台,满足人工智能、数据中心等对算力要求极高的应用场景的需求。例如Nvidia推出的GB200 Grace Blackwell 芯片和AMD推出的MI300系列产品等均采用了三维异质异构集成技术。

2)5G通信与毫米波频段应用,在5G通信和毫米波频段应用中,三维异质异构集成可以将射频前端模块、基带处理芯片、毫米波天线等集成在一起,形成高度集成化的5G毫米波通信系统,提高系统的集成度和性能。如美国国防部高级研究计划局(DARPA)的SMART项目,通过三维异质异构集成技术,实现一种超低剖面毫米波有源相控阵列(AESA)的系统集成架构。

3)物联网与传感器网络,通过异质异构集成技术,将不同类型的传感器(如温度传感器、湿度传感器、压力传感器等)与信号处理芯片、通信芯片等不同功能芯片集成在一起,形成一个完整的物联网传感器节点,实现对物理世界的实时感知和数据传输。

4)消费电子与智慧终端,如在智能手机、平板电脑等消费电子产品中,三维异质异构集成可以将处理器、存储器、摄像头、显示屏等不同功能的芯片和元件集成在一起,使产品更加轻薄、高性能、多功能。

发展现状

目前,全球三维异质异构微系统集成市场尚未形成明确的垄断格局,市场份额较为分散。2024年,全球异构集成市场(包含三维异质异构微系统集成)规模达到31.3亿美元。SiP行业也从传统2D封装逐渐过渡到以2.5D/3D封装以及三维异质异构为主的封装方式,数据显示,2024年,2.5/3D封装设计占比上升到25%,2D封装降至72%[2]。

近年来,以长电科技、通富微电、华进半导体等为首的国内企业不断在先进封装技术方面取得突破性成果。

1)长电科技,集合现有先进封装技术,推出面向Chiplet的高密度多维异构集成平台(XDFOI),利用协同设计理念实现芯片成品集成与测试一体化机,涵盖2D、2.5D、3D Chiplet集成技术。同步实现国际客户4nm节点多芯片系统集成封装产品出货。其2.5D/3D项目主要集中在长电微电子(江阴)有限公司、长电集成电路(绍兴)有限公司。

2)通富微电,拥有完整的高端集成电路组装和测试生产线,开发扇出型、圆片级、倒装焊、Chiplet、2D+、基于玻璃芯基板和玻璃转接板的 FCBGA 芯片封装技术等技术,具备大尺寸Fan-out、大尺寸2.5D先进封装小规模量产能力。已建有超大尺寸2.5D先进封装技术研发及产线建设项目、高带宽存储芯粒先进封装技术研发和产线建设项目。

3)华进半导体,华进半导体基于国家集成电路特色工艺及封装测试创新中心,已建成12吋兼容8吋的晶圆级封装中试线,并通过以企业为创新主体的产学研用相结合的模式,开展系统封装设计、2.5D/3D 集成、晶圆级扇出封装、大尺寸FCBGA封装、光电合封、混合键合、SiP封装等关键核心技术研发,为产业界提供知识产权、技术方案等相关服务。为支撑先进封装技术服务,开发了国内首套先进封装PDK套件。基于三维集成技术研发,2021年获国家科学技术进步奖一等奖;“基于有源硅转接板的晶圆级3D Chiplet集成技术,”荣获“2023中国电子信息影响力品牌榜”电子信息创新技术奖;基于“硅基光电晶圆端面耦合器与TSV一体化三维集成技术”,荣获2022年中国半导体行业协会第十五届中国半导体创新产品和技术奖。华进半导体开发的三维异质异构集成技术关键技术指标达国际先进水平。此外,建成包含芯片倒装焊、植球、系统测试等20余道工艺的柔性产线。

五、结语

未来,三维异质异构集成将继续朝着更高密度、更高性能、更低功耗、更小尺寸的方向发展。随着技术的不断成熟和成本的降低,其应用领域将进一步扩大,有望在更多新兴领域得到广泛应用,如数据中心、自动驾驶、量子计算等。同时,新材料、新工艺、新架构的不断涌现,也将为三维异质异构集成的发展提供新的机遇和挑战。

1. 智研咨询《研判2025!中国SIP行业生产工艺、市场规模、竞争格局及未来前景展望:SIP封装技术持续发展,引领电子封装新革命》https://www.chyxx.com/industry/1213445.html

2. Technology(2.5D, 3D, System-in-Package (SiP), Through Silicon Vias (TsV),Fan-Out Wafer Level Packaging,(FOWLP)and others),By component(Hardware,Software),By Material, By Application, and By Region, Forecast 2025-2032

https://navistratanalytics.com/report_store/heterogeneous-integration-market/

3.SSCC2025 | 从单片二维到异构集成:先进封装技术全景https://www.latitudeda.com/document/882

免责声明:市场有风险,选择需谨慎!此文仅供参考,不作买卖依据。

责任编辑:kj005